先决条件–执行, 阶段和吞吐量

每个指令周期涉及的寄存器:

- 内存地址寄存器(MAR):连接到系统总线的地址线。它指定内存中用于读或写操作的地址。

- 内存缓冲寄存器(MBR):连接到系统总线的数据线。它包含要存储在存储器中的值或从存储器中读取的最后一个值。

- 程序计数器:保存要提取的下一条指令的地址。

- 指令寄存器(IR):保存上一条提取的指令。

指令周期–

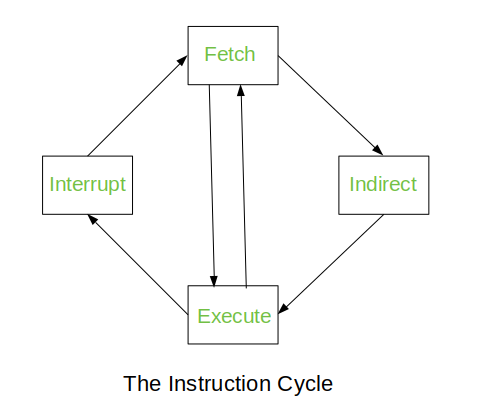

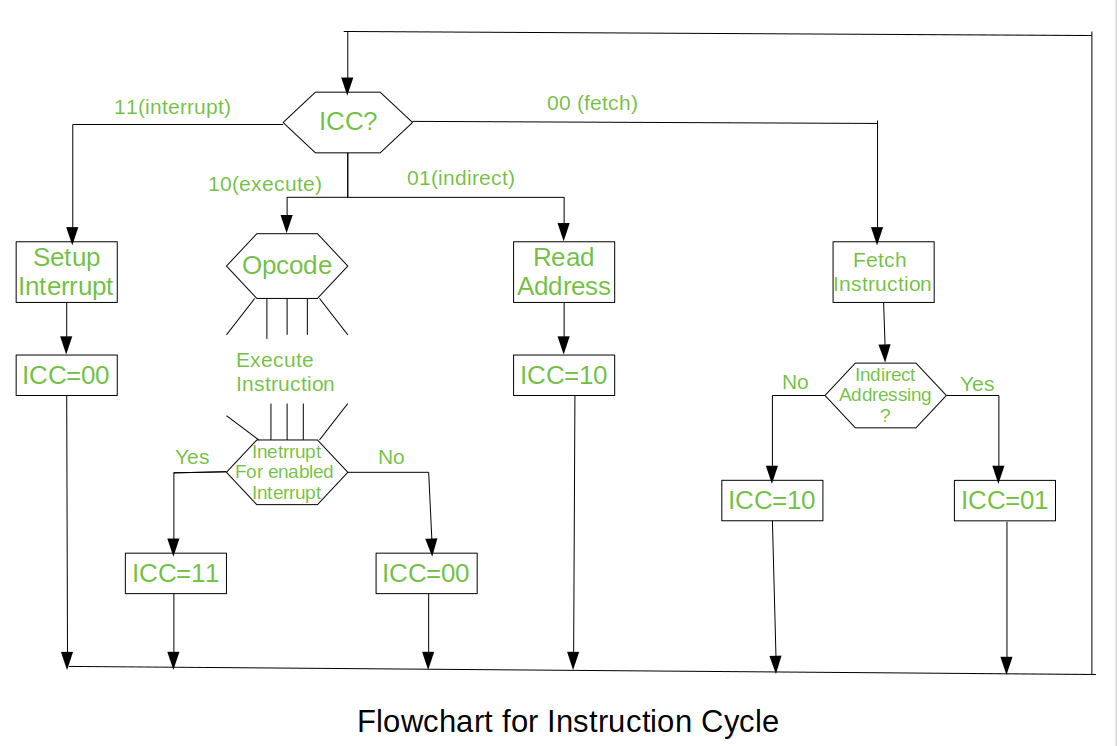

指令周期的每个阶段都可以分解为一系列基本的微操作。在上面的例子中,取、间接、执行和中断周期各有一个序列。

间接循环总是跟着执行周期。的中断周期总是跟着提取周期。对于获取和执行周期, 下一个周期取决于系统状态。

我们假设一个新的2位寄存器称为指令周期代码(ICC)。 ICC根据其处于周期的哪个部分来指定处理器的状态:

00:提取周期

01:间接循环

10:执行周期

11:中断周期

在每个周期结束时, ICC均已正确设置。指令周期仅根据指令序列和中断模式描述了微操作的完整序列(这是一个简化的示例)。处理器的操作被描述为一系列微操作的执行。

不同的指令周期:

提取周期–

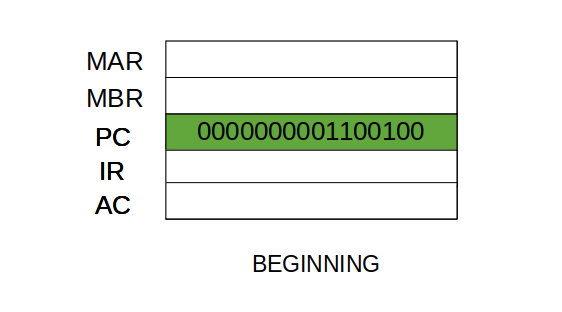

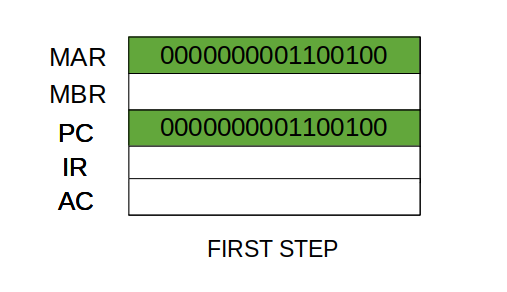

在获取周期的开始,下一条要执行的指令的地址在程序计数器(PC)中。

步骤1:程序计数器中的地址被移至存储器地址寄存器(MAR), 因为这是唯一连接到系统总线地址线的寄存器。

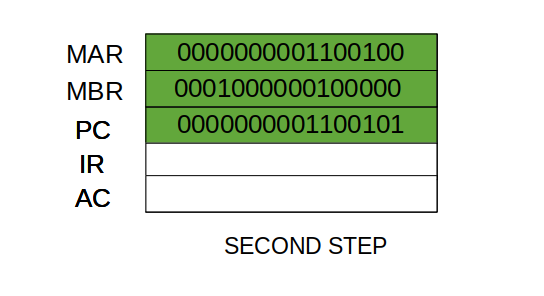

步骤2:将MAR中的地址放在地址总线上, 现在控制单元在控制总线上发出READ命令, 结果出现在数据总线上, 然后复制到内存缓冲寄存器(MBR)中。程序计数器加一, 以准备下一条指令。(可以同时执行这两个操作以节省时间)

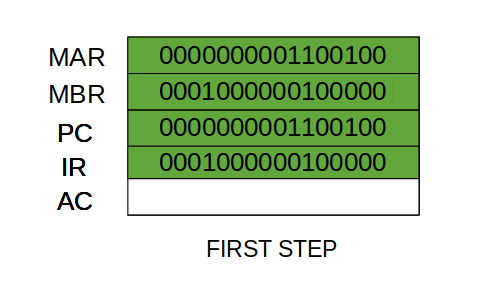

步骤3:将MBR的内容移至指令寄存器(IR)。

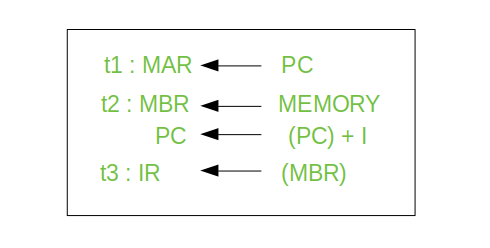

因此, 一个简单的提取周期包括三个步骤和四个微操作。象征性地, 我们可以将这些事件序列编写如下:

这里的”我”是指令长度。符号(t1, t2, t3)代表连续的时间单位。我们假设一个时钟可用于计时目的, 并且它会发出规则间隔的时钟脉冲。每个时钟脉冲定义一个时间单位。因此, 所有时间单位的持续时间相等。每个微操作都可以在单个时间单位的时间内执行。

第一时间单位:将PC的内容移至MAR。

第二时间单位:将MAR指定的存储位置的内容移至MBR。 PC的内容按I递增。

第三时间单位:将MBR的内容移至IR。

注意:

第二和第三微操作均在第二时间单元内进行。

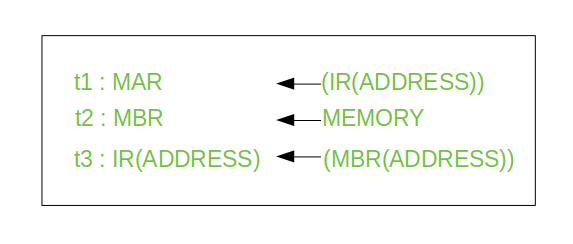

间接周期–

提取指令后, 下一步就是获取源操作数。源操作数正在通过间接寻址获取(可以通过任何方式获取寻址方式, 这里是通过间接寻址完成的。无需获取基于寄存器的操作数。一旦执行了操作码, 可能需要进行类似的处理才能将结果存储在主存储器中。以下微操作发生:-

步骤1:指令的地址字段被传送到MAR。这用于获取操作数的地址。

步骤2:从MBR更新IR的地址字段(因此它现在包含直接寻址而不是间接寻址)

步骤3:IR现在处于状态, 就好像尚未发生间接寻址一样。

注意:现在IR已准备好执行周期, 但它会跳过该周期片刻, 以考虑中断周期.

执行周期

其他三个周期(

提取, 间接和中断

)简单易懂。它们每个都需要简单, 小的和固定的微操作序列。在每种情况下, 每次都重复相同的微操作。

执行周期不同于它们。就像, 对于具有N个不同操作码的机器, 可能会发生N个不同的微操作序列。

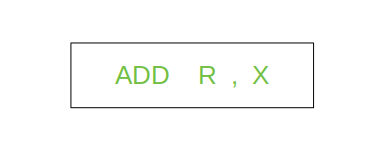

让我们假设一个例子:

考虑添加指令:

在这里, 此指令将位置X的内容添加到寄存器R。相应的微操作将是:

我们从包含ADD指令的IR开始。

步骤1:将IR的地址部分加载到MAR中。

步骤2:从MBR更新IR的地址字段, 以便读取参考存储器位置。

步骤3:现在, R和MBR的内容由ALU添加。

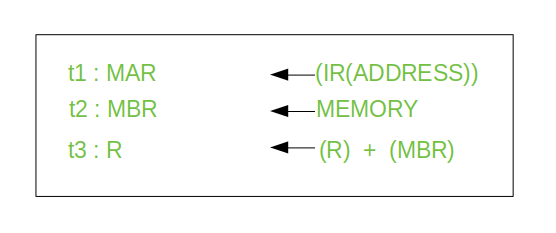

让我们举一个复杂的例子:

此处, 位置X的内容加1。如果结果为0, 则将跳过下一条指令。微操作的相应顺序为:-

在此, 如果(MBR)= 0, 则PC递增。此测试(MBR等于或不等于0)和动作(PC递增1)可以实现为一个微操作。

注意:可以在将更新值MBR存储回内存的同一时间单位内执行此测试和操作微操作。

中断周期:

在执行周期完成时, 将进行测试以确定是否发生了任何使能的中断。如果发生了允许的中断, 则发生中断周期。从一台机器到另一台机器, 这个周期的自然变化很大。

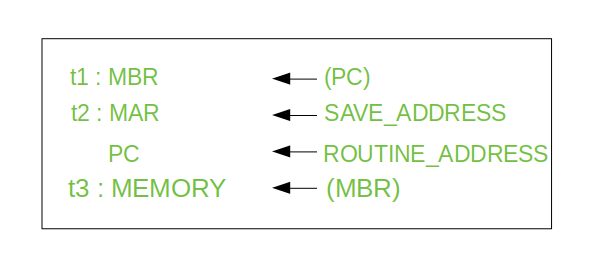

让我们进行一系列微操作:

步骤1:将PC的内容传输到MBR, 以便将其保存以供返回。

步骤2:MAR加载了要保存PC内容的地址。

PC装载了中断处理程序开始的地址。

步骤3:MBR(包含PC的旧值)存储在内存中。

注意:在步骤2中, 将两个动作实现为一个微操作。但是, 大多数处理器提供多种类型的中断, 在分别将它们分别传递到MAR和PC之前, 可能需要一个或多个微操作来获取save_address和例程例程地址。

来源:

https://www.srcmini02.com/69446.html